- Изучение VHDL

- Операции в выражениях

- Упрощение VHDL кода: тип данных std_logic_vector

- Зачем нам нужны типы данных векторы?

- Тип данных « Std_Logic_Vector »

- Интерпретация данных Std_Logic_Vector

- Восходящий или нисходящий индексный диапазон?

- VHDL, Ультракороткая справка — конспект

- Структура модуля (объекта)

- Entity

- Architecture

- Предопределенные типы и операторы

- User-Defined типы

- Примеры

- Операторы для Integer

- Операторы для Boolean

- Функции и процедуры

- Функции приведения типов

- Library and Package

- 1 — Структурное проектирование, Component

- Пример проверки на простое число:

- Пример инвертора шины:

- 2 — Потоковое проектирование, оператор «=>»

- 3 — Поведенческое проектирование, Process

- Последовательные циклы в процессе

- Задержки в процессе

Изучение VHDL

Операции в выражениях

В VHDL выражения выполняют арифметические или логические вычис-ле-ния над одним или несколькими операндами. Выражения используются в операторах присваивания сигналу, переменной, при присваивании начального значения, как операнд в других операторах, как входной параметр вызова процедуры или функции.

Операции VHDL перечислены в таблице 1 в порядке их приоритета.

Таблица 1 — Операции VHDL.

| Тип операции | Символ или ключевое слово |

| Логические Сравнения Сдвига Сложения Унарные (знак) Умножения Различные | and, or, nand, nor, xor, xnor =, /=, , >= sll, srl, sla, sra, rol, ror +, -, & (конкатенация) +, — *, /, mod, rem **, abs, not |

Логические операции имеют самый низкий приоритет. Операнды логических операций должны быть одного типа bit или boolean, или одномерного регулярного типа (векторы) из элементов типа bit или boolean. Для однозначной компиляции логических выражений необходимо использовать скобки, например:

Операции сравнения выполняются над операндами одинакового типа и возвращают тип boolean. Операции равенства ” = “ и неравенства ” /= “ выполняются над всеми типами. Остальные операции сравнения выполняются над перечисляемыми типами, целыми типами и одномерными регулярными типами (векторами) из элементов такого типа.

При сравнении перечисляемых типов элемент, стоящий в ряду правее (старший), считается большим. При сравнении векторов сравниваются пары элементов векторов, начиная с самых левых. Если пара элементов неодинакова, то вектор с более старшим элементом считается большим. Если пара элементов одинакова то рассматривается следующая пара элементов. Например, в сравнении векторов битов ”0111“ >= ”01011“ результат будет true.

Операции сдвига выполняют сдвиг вектора битов на число разрядов типа integer. Например, результатом выражения (”100110“ sra 3) является вектор ”111100“ , т.е. происходит арифметический сдвиг вправо на 3 разряда.

Операции сложения — вычитания ” + “, ” — “ предопределены для целых чисел и чисел с плавающей запятой. Операция конкатенции ” & “ применяется со всеми одномерными регулярными типами или с их элементами. С помощью этой операции векторы — операнды объединяются в более длинные векторы. Например, выражение ”101“ & ‘1’ & ”10“ даст результат ”101110“.

Унарные операторы применяются к одиночным операндам. Оператор минус инвертирует значение операнда. Операторы умножения ” * “, деления ” / “ применяются с целыми операндами и операндами с плавающей запятой. Операторы mod (модуль), rem (остаток) применяются с целыми числами. Операции абсолютного значения abs и возведения в степень ” ** “ определены для целых чисел и чисел с плавающей запятой, причем показатель степени должен быть целым.

Для многих операций языка существуют функции с таким же обозначением. Эти функции выполняют аналогичные действия, что и операции, но над другими типами. Например, функция ” + “ из пакета numeric_bit библиотеки IEEE выполняет сложение векторов битов, которые кодируют целые числа. Такие функции перезагружают операции в зависимости от типа операндов.

При программировании для синтеза следует учесть, что правый операнд для операций ” / “, mod, rem может быть равным только степени двойки, а левый операнд операции ” ** “ должен быть равен 2, так что эти операции будут означать сдвиг двоичного кода.

Упрощение VHDL кода: тип данных std_logic_vector

В данной статье будет рассмотрен тип данных «std_logic_vector», который является одним из наиболее распространенных типов данных в VHDL.

В предыдущей статье о языке описания аппаратуры VHDL мы обсудили базовую структуру кода VHDL с помощью нескольких вводных примеров. В данной статье мы рассмотрим один из наиболее распространенных в VHDL типов данных, т.е. тип данных « std_logic_vector ».

Сначала мы обсудим тот факт, что векторы позволяют нам иметь более компактное и читаемое описание VHDL, особенно при работе с большими схемами. Затем, рассмотрев некоторые важные особенности типа данных « std_logic_vector », мы рассмотрим некоторые стили кодирования, которые помогут нам избежать ошибок при использовании векторов.

Зачем нам нужны типы данных векторы?

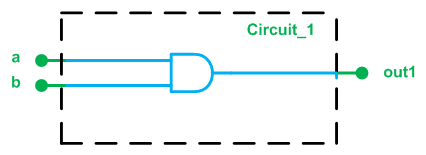

Рассмотрим простую схему на рисунке 1, которая обсуждалась в предыдущей статье.

Ниже показан VHDL код для этой схемы.

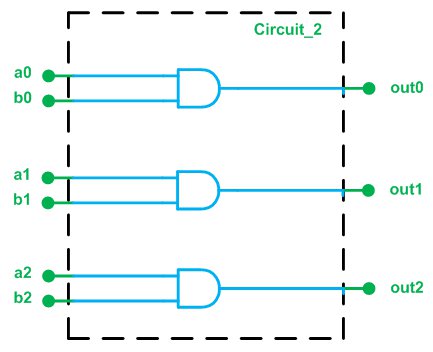

Теперь предположим, что нам необходимо написать VHDL код для схемы на рисунке 2.

Чтобы получить VHDL описание рисунка 2, мы можем расширить предыдущий код подобным образом:

Приведенный выше код верен; однако мы увидим, что для этой схемы возможно иметь более компактное и читаемое описание VHDL. Недостатком вышеуказанного кода является то, что он представляет каждый из портов ввода/вывода в виде отдельных сигналов и не устанавливает никакой связи между ними.

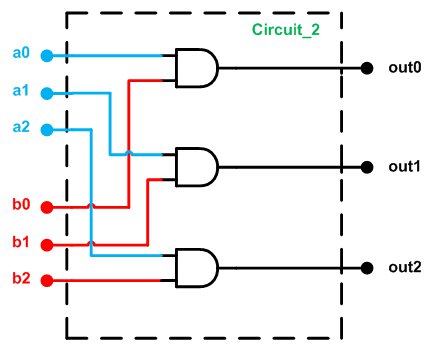

Рассмотрим альтернативный способ отображения схемы на рисунке 2.

Рисунок 3 предполагает, что мы можем рассматривать a0 , a1 и a2 как трехбитовый входной порт, под названием, например, a_vec . Аналогично, входные порты b0 , b1 и b2 могут быть сгруппированы как еще один трехбитовый входной порт под названием b_vec . То, что делает схема, – это выполнение операции И элемента a_vec с соответствующим элементом b_vec . Это может показаться простой идеей, но через минуту мы увидим, как этот способ мышления делает код более удобочитаемым.

Тип данных « Std_Logic_Vector »

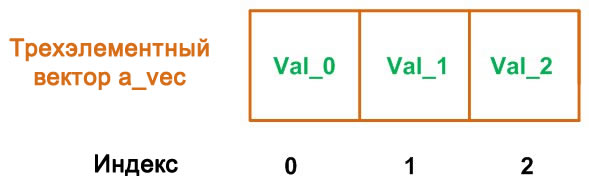

Чтобы представить группу сигналов, VHDL использует векторные типы данных. Чтобы получить доступ к элементу вектора, нам нужно определить индекс. Например, предположим, что, как показано на рисунке 4, мы используем вектор с длиной три, чтобы представить три значения: val_0 , val_1 и val_2 . Чтобы получить доступ к значению элемента из этого вектора, мы можем использовать номера индексов. Например, a_vec(2) даст значение самого правого элемента вектора на рисунке 4, которое равно val_2 .

Ключевое слово VHDL « std_logic_vector » определяет вектор элементов типа std_logic . Например, std_logic_vector(0 to 2) представляет собой трехэлементный вектор типа данных std_logic , причем диапазон индексов распространяется от 0 до 2.

Давайте, используем тип данных « std_logic_vector » для описания схемы на рисунке 3. Мы будем использовать три вектора a_vec , b_vec и out_vec для представления соответственно синих, красных и черных портов на рисунке 3. С новым названием портов мы получим следующий рисунок.

VHDL код для рисунка 5 будет следующим.

Строки 4-6 данного кода используют тип данных « std_logic_vector » для портов ввода/вывода схемы. Обратите внимание, что операция И в строке 11 будет применена к соответствующим элементам двух векторов a_vec и b_vec , т.е. a_vec(0) логически умножается на b_vec(0) , и результат присваивается out_vec(0) , и так далее. Сравнивая это с предыдущим кодом, мы наблюдаем, что использование типа данных « std_logic_vector » позволяет нам иметь гораздо более компактный и читаемый код. Это преимущество становится особенно очевидным при работе с большими схемами; просто представьте, насколько громоздким будет код, если бы мы использовали отдельные инструкции присваивания сигналов для выполнения логической операции И с элементами двух 32-разрядных векторов.

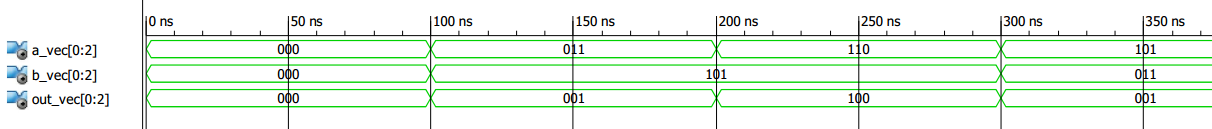

Моделирование ISE приведенного выше кода показано на рисунке 6.

Интерпретация данных Std_Logic_Vector

Существует один важный момент, который требует дополнительного внимания. Как показано в приведенном выше примере, тип данных « std_logic_vector » – это способ представления группы сигналов или шины данных. Это просто строка из единиц и нулей, и нет никакой другой интерпретации для этой строки из единиц и нулей. Другими словами, если мы присвоим » 011 » вектору a_vec , это не означает, что a_vec равен 3 (десятичный эквивалент » 011 «).

Мы не можем считать вес для разных позиций битов сигнала « std_logic_vector ». Однако мы можем использовать функции преобразования типов и приведение типов, чтобы интерпретировать строку из единиц и нулей в данном сигнале « std_logic_vector » как число. Преобразование типа будет обсуждаться в следующей статье.

Восходящий или нисходящий индексный диапазон?

До сих пор мы использовали тип данных std_logic_vector при определении портов ввода/вывода. Аналогично, мы можем определить сигнал типа std_logic_vector . В качестве примера рассмотрим следующие строки кода:

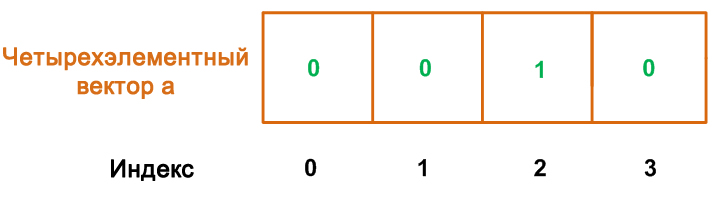

Здесь первая строка определяет сигнал типа « std_logic_vector ». Индекс находится в диапазоне от 0 до 3. Затем a присваивается » 0010 «. С этим присваиванием, как показано на рисунке 7, мы будем иметь a(0)=0 , a(1)=0 , a(2)=1 и a(3)=0 .

Стиль индексации данного вектора, который использует ключевое слово « to », называется восходящим. Мы также можем использовать ключевое слово « downto » (вместо « to »), когда нам нужен нисходящий индексный диапазон.

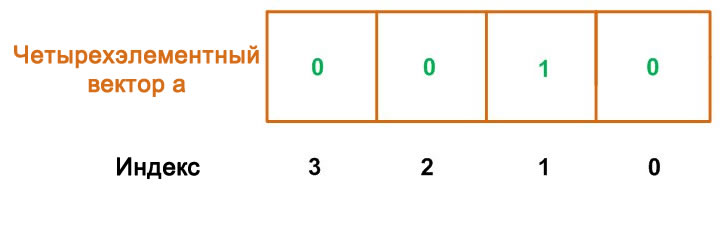

В этом случае, как показано на рисунке 8, мы будем иметь a(3)=0 , a(2)=0 , a(1)=1 и a(0)=0 .

Выбор между восходящим и нисходящим порядком часто связан с предпочтениями разработчика, хотя он может быть рассмотрен в руководстве по кодированию, принятом конкретной организацией. Самое главное – выбрать один стиль, а затем последовательно следовать ему; смешивание двух разных стилей в одном проекте может легко привести к проблемам.

Например, рассмотрим таблицу истинности для приоритетного шифратора 4-к-2, показанную ниже. Для приоритетного шифратора мы обычно рассматриваем самый левый бит входного вектора как с самым высоким приоритетом. Например, в следующей таблице истинности, когда самый левый входной бит x(3) равен логической единице, нам не важны состояния остальных трех входных битов, и мы устанавливаем выходы y и v , т.е. y=»11″ и v=»1″ .

| Входы | Выходы | |||||

|---|---|---|---|---|---|---|

| x(3) | x(2) | x(1) | x(0) | y(1) | y(0) | v |

| 1 | не важен | не важен | не важен | 1 | 1 | 1 |

| 0 | 1 | не важен | не важен | 1 | 0 | 1 |

| 0 | 0 | 1 | не важен | 0 | 1 | 1 |

| 0 | 0 | 0 | 1 | 0 | 0 | 1 |

| 0 | 0 | 0 | 0 | 0 | 0 | 0 |

Мы видим, что эта таблица истинности предполагает, что входной вектор x имеет нисходящий индексный диапазон, потому что элемент с самым высоким индексом помещается в крайнее левое положение. Предположим, что, несмотря на выбор нисходящего индекса в таблице истинности, мы используем восходящий индексный диапазон при объявлении входного вектора x и присваиваем x значение » 0001 «. Другими словами, мы имеем:

Так как самый правый бит x равен логической единице, учитывая общее определение приоритетного шифратора, мы ожидаем, что выходы y и v будут соответственно раны “ 00 ” и ‘ 1 ’. Однако, так как в приведенном выше коде логической единице равен x(3) , основываясь на приведенной выше таблице истинности, выход будет равен y=“11” и v=‘1’ . Чтобы избежать таких проблем, мы должны последовательно использовать нисходящий индексный диапазон во всем коде.

VHDL, Ультракороткая справка — конспект

Структура модуля (объекта)

Entity

Architecture

Тело архитектуры представляет собой ряд параллельных операторов — concurrent_statement. Все параллельные операторы в теле архитектуры исполняются одновременно!

Самым главным параллельным оператором является оператор component. Для каждого оператора component в теле архитектуры создается копия объекта, которая должна иметь уникальную метку label.

Предопределенные типы и операторы

User-Defined типы

Примеры

Операторы для Integer

Операторы для Boolean

Функции и процедуры

Функции приведения типов

Library and Package

При создании проекта автоматически создается библиотека work, неявно в начале файла помещается «library work;». Можно поменять — library (library_clause), например library ieee;

Package — файл, содержащий определения элементов, которые могут быть использованы другими программами. Пакет может включать сигналы, типы, константы, функции, процедуры, объявления компонентов.

Подключение пакета, всего или отдельного определения:

1 — Структурное проектирование, Component

Пример проверки на простое число:

Пример инвертора шины:

2 — Потоковое проектирование, оператор «=>»

Это Описание схемы в терминах потока данных и выполняемых схемой операций над этими данными.

Параллельный сигнальный оператор присваивания:

Пример проверки на простое число:

или с условиями

или с использованием select

или с использованием конвертации в Integer

3 — Поведенческое проектирование, Process

Процесс всегда либо выполняется, либо приостановлен. Перечень сигналов (sensitivitty_list) задает условия, когда процесс выполняется. Первоначально процесс остановлен.

ОПЕРАТОРЫ выполняются внутри ПРОЦЕССА ПОСЛЕДОВАТЕЛЬНО! Оператор ⇐ в процессе — это последовательный оператор присваивания! Для переменных это оператор := .

тоже с приведением к Integer

тоже с оператором выбора

Последовательные циклы в процессе

Задержки в процессе

Задержка 4нс при переходе выхода из 0 в 1, и 3нс при переходе из 1 в 0: